| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

- 딥러닝

- DRAM

- SpMM

- GPU

- 반도체

- jhDNN

- sycl

- CuDNN

- Qubit

- CUDA

- nvidia

- stl

- POD

- kubernetes

- Compression

- cloud

- 쿠버네티스

- jhVM

- HA

- C++

- deep_learning

- 양자역학의공준

- flash_memory

- quantum_computing

- Semiconductor

- convolution

- 반도체기초

- dnn

- FPGA

- 클라우드

- Today

- Total

Computing

반도체 선폭과 공정(14nm, 10nm, 7nm 공정의 의미) 본문

선단 공정과 반도체 선폭

14nm 공정, 10nm 공정, 7nm 공정, 3nm 공정 까지. 반도체 공정은 이렇게 숫자를 이용해서 명칭되며, 숫자가 작아질수록 더 고도화된 선단 공정을 의미한다 (공정이 미세화된다고 함). 현재, 최신 프로세서의 경우 10nm, 7nm가 메인이며 3nm 수준의 공정이 개발 및 3nm 공정을 이용한 양산이 시작되고 있다.

반도체 공정을 설명하는 이 나노미터 숫자는 일반적으로 채널의 길이 (Fig 1. Channel Length) 혹은 회로의 선폭(Fig 2. Metal 배선과 배선과의 최소 거리, half-pitch) 을 의미한다. (후술하겠지만 이제는 일치하지 않는다고 함[3,4])

Fig 1.에서 주황색 화살표(Channel Length)가 줄어들수록 트랜지스터의 크기는 감소한다. 혹은 Fig 2. 에서 선과 선 사이의 거리 (Half-pitch)가 감소하면 선들을 촘촘히 배치할 수 있다. 따라서 공정이 미세화될수록 같은 크기의 영역에 더 많은 트랜지스터와 회로를 넣을 수 있다고 한다.

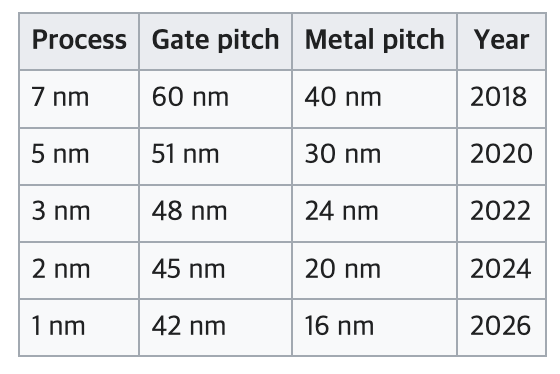

다만 최근에는 공정의 숫자가 채널의 길이와 회로의 선폭과 정확히 일치하지 않고, 단순 최신 세대를 나타내는 마케팅 용어로 쓰인다고 한다[3][4]. 밑의 Table 1.은 공정별 예상되는 Pitch의 길이를 나타낸 숫자로 7nm 공정은 대략 40nm 정도 Pitch (Half-Pitch는 20nm)를 가진다. 이 수치 또한 트랜지스터의 종류 (MOSFET, FINFET, GAA...), 제조사 (TSMC, SEC, Intel..) 에 따라서도 달라진다고 한다.

Reference

[1] https://news.skhynix.co.kr/post/short-channel-effect

[2] https://www.tel.com/museum/magazine/material/150227_report04_01/

'Semiconductor > 반도체공정' 카테고리의 다른 글

| 반도체 제조 공정 단계별 정리 (웨이퍼 제조, 프론트엔드, 백엔드 공정) (0) | 2024.05.11 |

|---|---|

| [DRAM] DRAM 제품 세대 명칭 (1a, 1b, 1c.. 공정) (0) | 2024.04.21 |

| 반도체 8대 공정 요약 정리 (0) | 2022.04.20 |