| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

- DRAM

- CUDA

- 딥러닝

- Qubit

- deep_learning

- 반도체기초

- kubernetes

- HA

- quantum_computing

- convolution

- Compression

- 반도체

- POD

- flash_memory

- 클라우드

- SpMM

- jhDNN

- nvidia

- FPGA

- jhVM

- Semiconductor

- 양자역학의공준

- 쿠버네티스

- sycl

- dnn

- stl

- C++

- GPU

- CuDNN

- cloud

- Today

- Total

Computing

FPGA Design Concepts - 1 : Overview 본문

High Level Languages for FPGA Programming

Intel ® oneAPI DPC++ FPGA Optimization Guide[1]를 참고하여 FPGA 기본 design concepts을 정리하고자 한다.

일반적으로 FPGA를 프로그래밍하는 방법은 Verilog나 VHDL과 같은 하드웨어 기술 언어(HDL)를 이용하여 프로그램 로직을 구현하는 것이다. 최근에는 OpenCL, SYCL 등 high level language를 사용해서 좀 더 쉽게 FPGA 프로그램 개발이 가능해지고 있으며, 이러한 방식이 대세가 되고 있다고 한다.

HDL을 사용하지 않고 high level language를 사용하여 FPGA 프로그램을 구현할 경우 하드웨어를 잘 몰라도 쉽게 구현할 수 있다. SYCL로 통해 FPGA 프로그램을 개발하면 register, memory를 언제 읽어야 하고, logic은 어떻게 구현해야 하고 등등 하드웨어를 잘 모르더라도 DPC++ 컴파일러가 알아서 다 해준다. 따라서 FPGA 프로그램도 일반 CPU, GPU 프로그래밍 방식처럼 개발할 수 있다. 특히 SYCL의 경우 CPU, GPU에서 돌아가는 코드 그대로 FPGA에서 돌아가는 것(코드 이식성)뿐만 아니라 최적의 성능까지도 달성(성능 이식성)할 수 있도록 개발되고 있다.

그렇지만 여전히 OpenCL이나 SYCL 등의 high level language를 이용한 FPGA 개발에서 FPGA의 기본 아키텍처를 이용하는 것은 최상의 성능을 달성하기 위해서 필수라고 한다. GPU 프로그래밍에서 memory 개념 (coalesced memory access, shared memory bank conflict, etc.), warp 개념 (branch divergence, synchronization, etc.), tensor core 등 여전히 GPU 하드웨어를 알아야 프로그래밍 튜닝이 가능한거과 비슷한 맥락일 것 같다.

따라서 이번 포스팅에서는 FPGA architecture의 대략적인 개념을 정리하고자 한다.

FPGA 개발 특징

FPGA는 Fleid Programmable Gate Array의 약자로, reconfigurable 반도체 IC이다. 따라서 특정 문제를 해결하기 위한 로직으로 FPGA 회로를 reconfigurate할 수 있다. 따라서 CPU, GPU와 같은 회로가 고정된 IC보다는 특정 문제 해결에 더 효율적일 수 있다. ASICs와 같이 생산 때부터 특정 문제를 위해 설계된 IC보다는 계산과정이 비효율적일 수 있지만, 프로그램에 변경이 발생할 시 변경된 프로그램으로 다시 빌드하면 되고, 아예 다른 프로그램으로 reconfigurate하여 다른 목적으로 재사용할 수도 있어서 운영 시 전체적인 비용이 줄어든다고 한다.

FPGA Architecture Overview

FPGA는 spatial architecture라고 하며 CPU와 GPU와 같은 ISA-based architecture와는 매우 다르다고 한다. 일반적으로 우리가 아는 CPU(GPU)는 instruction을 Fetch-Decode-Execute 하여 프로그램(A set of instructions)울 실행한다. CPU(GPU) 회로는 고정되어 있으며 general purpose를 위해 여러 회로가 미리 구현되어 있다. 프로그램 실행 시 instruction(control)에 따라 데이터를 특정 datapath에 통과시켜 결과를 얻는다.

그에 비해 FPGA는 spatial architecture라고 하는데, 칩 상의 공간에 회로를 설계하고 이 회로에 데이터가 입력으로 들어가 처리되어 최종 결과로 나온다. 따라서 FPGA 칩 위에 회로를 빌드되어야 프로그램이 실행되기에, FPGA 칩은 임의의 회로를 구성할 수 있게 다양한 building block으로 구성된다.

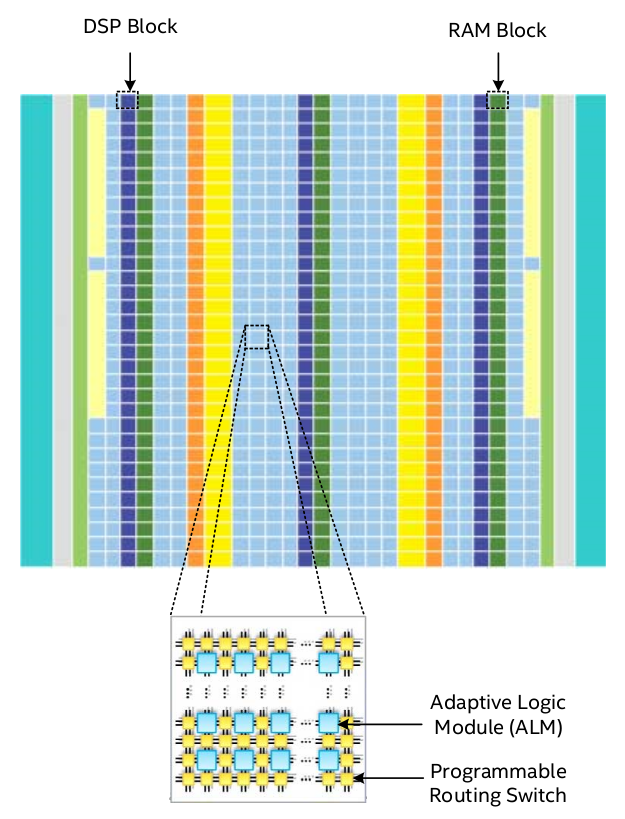

FPGA는 ALMs(Adaptive Logic Module, configurable logic), 특수 기능 수행을 위해 추가된 DSP blocks(Digital Signal Processig) RAM(Random Access Memory) block으로 구성된다. 이 block들을 연결하여 하나의 회로를 구성하기 위한 configurable routing interconnects도 포함된다. 이 ALMs, DSP blocks, RAM blocks들을 통틀어 FPGA area라고 한다.

Refenrence

'가속기 Accelerator > FPGA' 카테고리의 다른 글

| OpenCL on FPGA (1) 필요성과 Intel FPGA SDK for OpenCL (0) | 2022.05.30 |

|---|---|

| FPGA via SYCL - 1 : Tutorial 빌드 및 실행 in DevCloud (0) | 2022.05.02 |

| FPGA Design Concepts - 2 : Building blocks (3) | 2022.03.24 |