| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

- Qubit

- POD

- jhVM

- jhDNN

- CUDA

- kubernetes

- nvidia

- C++

- 반도체기초

- DRAM

- CuDNN

- SpMM

- sycl

- flash_memory

- stl

- HA

- cloud

- Compression

- 양자역학의공준

- dnn

- convolution

- 쿠버네티스

- Semiconductor

- 딥러닝

- 반도체

- 클라우드

- FPGA

- deep_learning

- quantum_computing

- GPU

- Today

- Total

Computing

DRAM Memory Organization - 1 : 소개 본문

Main Memory Subsystem

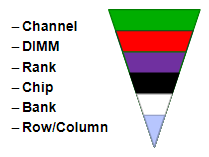

Fig 1.은 CPU가 어떻게 메모리에 접근하는 지를 간략히 잘 나타내고 있다. CPU는 code를 실행할 때, virtual memory address 기준으로 실행한다. Virtual address는 CPU 내의 memory management unit(MMU)에 의해서 physical address로 translate된다. Physical address를 이용해 memory controller는 main memory(DRAM)에 저장된 데이터의 실제 위치를 계산해낸다. 이때 main memory는 다음과 같은 계층 구조로 데이터 저장 시스템을 이루고 있다.

Fig 2. memory system 구조도는 memory가 어떤 계층으로 구성되는 지를 보여준다. 이번 포스터에서는 각각의 계층에 대하여 소개하자고 한다.

Overview

Fig 3. 는 메모리 시스템 구조 및 data bus의 width를 잘 보여준다. CPU는 memory controller (MC)를 통해 메인 메모리의 데이터에 접근한다. Fig 3의 메인 메모리는 multi channel 메모리 구조를 가지고 있는데(여기서는 2개), MC는 각 channel별로 독립적으로 DIMM(s)에 명령을 내리고 데이터에 접근할 수 있다. 각 channel은 여러개의 DIMMs(여기서는 2개)로 구성되며, 실제 메인모드에는 여러 개의 DIMM들을 꽂을 수 있는 slot을 볼 수 있다. DIMMs은 여러 개의 DRAM 칩으로 구성되며 8개의 칩이 하나의 rank를 구성한다. 메모리 용량이 커질수록 DIMM에 칩이 많이 붙는데, 8개씩 rank를 이뤄 한 DIMM 내에서 multi rank를 구성한다. Rank들끼리는 독립적으로 작동하지만 하나의 channel bus(DIMM과 CPU 사이)를 공유한다. Chip은 여러 개의 bank(여기서는 4개)로 이루어지며 bank 또한 DRAM chip의 data bus를 공유한다. Bank는 여러개의 arrays로 구성되며(여기서는 2개), 한 bank내 arrays도 bank의 data bus를 공유한다. arrays는 실제 bit(전기 정보)가 저장되는 DRAM cell들의 2차원 배열로 구성된다.

Channel & DIMM

Fig 4는 main memory system에서의 memory channel과 DIMM 구조를 자세히 보여준다. Memory controller(MC)의 성능에 따라 1, 2채널, 최근에는 4채널로 메인 메모리 시스템을 구성할 수 있다. 각 채널은 서로 독립적으로 작동하며 MC는 각 채널별로 데이터 접근을 독립적으로 할 수 있기에, 2채널의 경우 memory bandwidth가 2배가 되는 효과가 있다. 각각의 memory channel은 64bit 크기 bus를 가지므로 Fig 4.는 128bit 크기 bus를 가진다. 각 채널에는 여러 개의 DIMM이 부착될 수 있는데, 한 channel에 구성된 DIMM들끼리는 그 channel을 공유하기에 multi-channel과 같은 bandwidth가 커지는 효과는 없다.

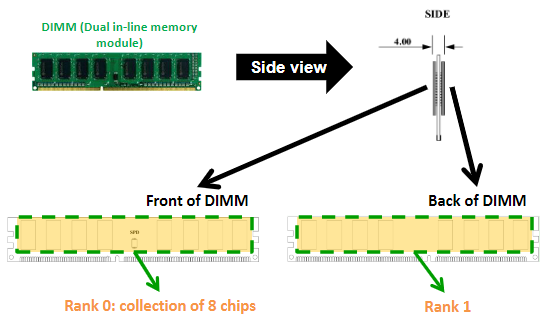

Rank & Chip

DIMM은 여러 개의 칩으로 구성된다. 주로 DIMM의 앞, 뒤에 칩이 붙으며, 1행 2열 혹은 2행 8열, N행 8*M열로 구성된다(ECC 메모리의 경우 9*M열). 1행의 8개 칩씩 하나의 rank를 구성한다. Fig 5.의 bus 구성을 보면 DIMM은 64bit data bus를 가지는데, 이 bus를 모든 rank가 공유한다. Rank를 구성하는 각각의 칩은 8 bit width bus를 독립적으로 차지한다. 따라서 한 rank 내 각각의 칩들은 병렬로 데이터 전송이 가능하다. (아직 추측인데, double precision floating point 64bit 저장 시 8bit씩 각 chip에 나눠서 저장되는 게 아닐까 싶다. 찾아봐야 겠다.)

Bank

Chip은 여러 개의 bank들로 구성된다. Chip은 8bit width data bus를 가지고 있으며 각각의 bank는 mux를 통해 chip의 data bus를 공유한다.

Array, Row & Column, Cell

Bank는 이제 실제 bit가 저장되는 cell들의 2차원 array로 구성된다. DRAM cell은 하나의 transistor와 하나의 capacitor로 구성되다. Capacitor는 실제 전기 신호가 저장되는 요소이며(high 전압이 걸리면 1, low 전압이 걸리면 0), transistor는 해당 cell에 접근할 지 말지를 결정하는 switch이다. DRAM cell들은 word-line과 bit-line으로 연결되며 word-line에 의해 transistor(switch)가 작동한다. Cell aray의 row는 word-line, column은 bit-line이라 한다. 추가적으로 Fig 3.에서 보듯, 한 bank는 여러 개의 cell array로 구성될 수 있는데, 각 cell array(sub-array라고도 함)는 bank의 8bit width data bus를 공유한다.

Reference

[1] Sudeep Pasricha, ECE 554 Computer Architecture Lecture 5, Colorado State University, Spring 2013

[2] Wei, R.; Li, C.; Chen, C.; Sun, G.; He, M. Memory Access Optimization of a Neural Network Accelerator Based on Memory Controller. Electronics 2021, 10, 438.

[3] https://www.equestionanswers.com/arm-fpga-interfacing/ARM-Cache-MMU.php

'Semiconductor > RAM' 카테고리의 다른 글

| SRAM 구조 및 읽기와 쓰기 방법 (0) | 2022.07.22 |

|---|---|

| DRAM Memory Organization - 2 : 성능 향상 전략 (0) | 2022.03.31 |

| RAM 메모리 : DRAM vs SRAM (2) | 2022.03.25 |