| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

- Semiconductor

- jhDNN

- Qubit

- stl

- deep_learning

- 클라우드

- 반도체

- DRAM

- SpMM

- nvidia

- sycl

- 딥러닝

- jhVM

- GPU

- CUDA

- FPGA

- quantum_computing

- flash_memory

- Compression

- 쿠버네티스

- 반도체기초

- POD

- dnn

- HA

- 양자역학의공준

- convolution

- cloud

- kubernetes

- CuDNN

- C++

- Today

- Total

Computing

DRAM Memory Organization - 2 : 성능 향상 전략 본문

DRAM Memory System Organization

2022.03.27 - [Semiconductor/메모리반도체] - DRAM Memory Organization - 1 : 소개

이전 포스터에서 DRAM memory system의 구성에 대해서 알아 보았다.

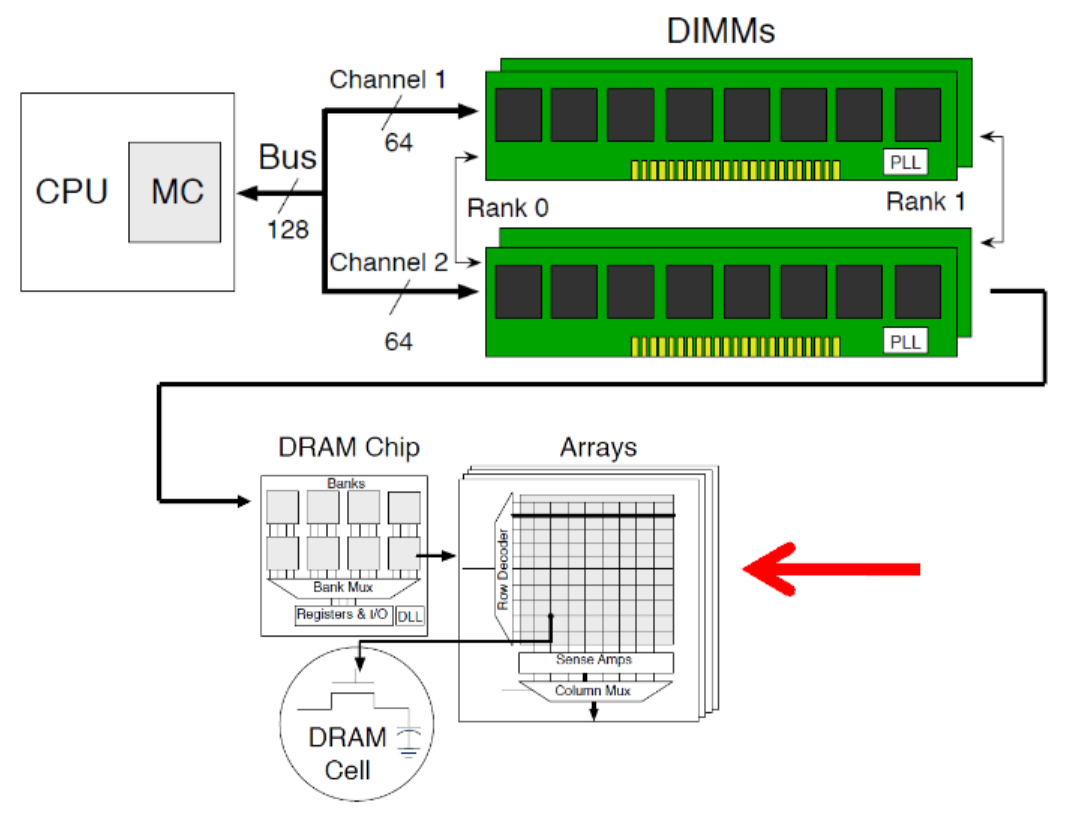

Fig 1.은 DRAM memory system을 요약한 것이다. 그림에서 보듯 DRAM system은 Channel-DIMM-Rank-Chip-Bank-Array의 순서로 hierarchically 구성된다. 이렇게 복잡한 계층 구조를 가지고 설계된 이유는 memory wall (CPU와 메인 메모리 간의 데이터 전송 병목에 의한 성능 향상 한계)를 극복하기 위해, DRAM 속 데이터를 병렬로 접근할 수 있도록 하기 위해서 이다. 오늘은 이러한 계층 구조 및 데이터 접근 병렬성에 대하여 [2] 자료를 참고하여 분석해본다.

기본 DRAM Array Access 분석

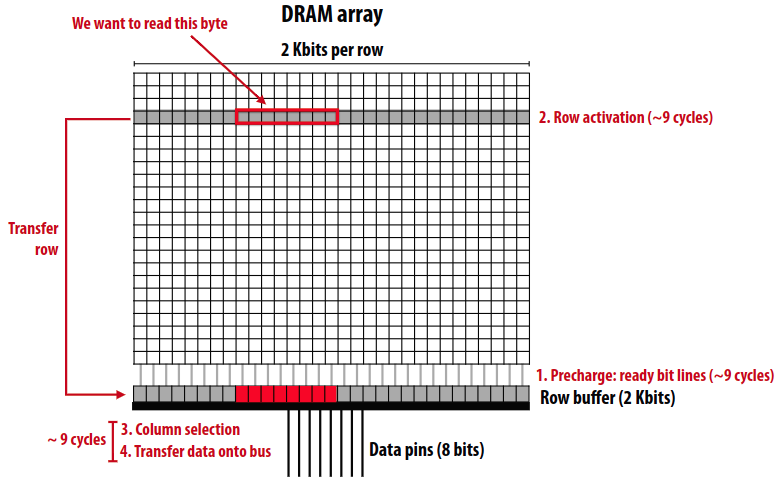

DRAM cell은 DRAM chip 내에 2차원 배열로 구성되며, row, column 번호를 이용해 각 cell의 주소가 정해진다. Row 방향을 word-line, column 방향을 bit-line이라고 한다. Column 방향으로 이웃하게 한 byte가 저장되는데, 따라서 Fig 2.의 빨간 박스는 하나의 Byte(=8 bits)를 나타낸다. 그림의 보면 cell 배열 뿐만 아니라 row buffer라는 것도 존재한다. Cell 데이터를 읽기 위해서는 cell에 직접 접근해서 읽는 것이 아닌 row buffer를 통해서 읽어야 한다. 즉 읽고자 하는 cell의 row를 row buffer로 복사해온 후, row buffer에서 데이터를 선택하고 data pins을 통해 CPU로 전송한다. 이 과정을 정리하면 다음과 같다.

- Row buffer 백업 : 이미 row buffer에 저장된 데이터를 원래의 row에 다시 저장한다.

- bit line precharge

- Row activation : 읽고자하는 row를 활성화 시킨다. 해당 row의 데이터는 row buffer에 저장된다.

- Column selection : row buffer에서 원하는 column을 선택한다. 이때 8 bit 단위로 선택된다.

- Transfer data onto bus : 선택된 1 byte (8 bits)를 data pins을 통해 전송한다.

DRAM Array Access : Burst Mode

다음 그림은 메모리 접근 예시이다. 파랑, 주황, 초록, 보라 btye를 하나씩 읽는다고 가정하면 single mode 그림과 같은 타임라인이 그려질 것이다. PRE는 precharge를, RAS는 row activate, CAS는 column access를 나타낸다. 한 byte를 읽기 위해서는 precharge(PRE)하고, row activate(RAS)하고, 마지막으로 column access(CAS)를 해야 한다. (Row buffer backup은 제외)

파랑 byte을 읽기 위해서는 해당 PRE하고 해당 row를 row buffer로 읽어온다(RAS). 이후 파랑 byte만 읽어서 전송(CAS)한다. 주황의 경우 이미 해당 row가 row buffer에 있기에 CAS만 실행한다. 초록과 보라는 각기 다른 row에 있기에 파랑과 같이 PRE-RAS-CAS를 실행한다. 이 예제에서 보면 알듯, 한 row에 있는 데이터를 연속해서 접근할 경우, PRE와 RAS가 생략되어 빠르게 데이터 전송이 가능하다. 따라서 만약 여러 byte를 전송해야 할 경우 한 row에 포함된 byte들끼리 모아서 데이터를 전송하도록 스케쥴링하면 빠른 데이터 전송이 가능할 것이다.

Mmemory controller와 DRAM은 이런 관점에서 burst mode를 지원한다. CPU는 cache를 이용해 data latency를 줄이는데, 이를 위해 (일반적으로) 64 byte cache line을 구성하고 1byte만 필요로 하더라도 64 byte를 한번에 읽어오도록 설계되었다. DRAM도 이를 지원하도록 1byte를 읽더라도 연속한 8 byte들을 연속해서 CPU로 전송한다. 이를 burst mode라고 한다. 이 경우에는 8 bytes에 대하여 한번의 PRE+RAS만 있으면 되기에 빠른 데이터 전송이 가능해 진다.

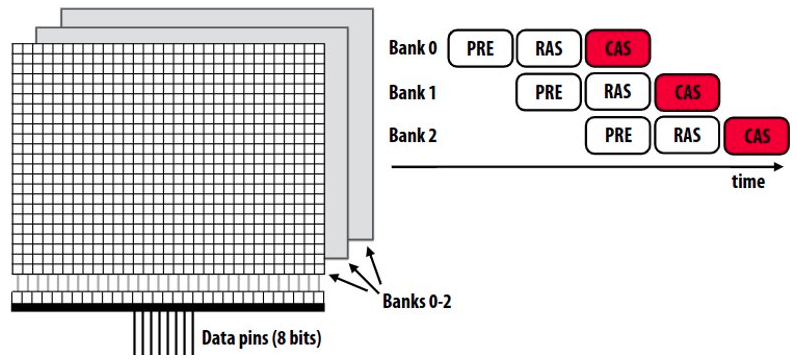

Chip : Multi-bank Structure

Burst 모드를 활용하더라도 PRE, RAS를 아예 제거할 수 없으며, RPE, RAS 동안에는 data pins(bus)가 idle하기에 매우 비효율적이다. 이를 극복하기 위해 DRAM chip은 여러 개의 bank들로 구성되어, data bus를 공유하도록 디자인되었다. 이를 통해 데이터 접근의 병렬성을 달성하였다. 그림 Fig 4.를 보면 bank들끼리 mux되어 data bus가 쉬지 않고 계속 일을 하는 것을 알 수 있다.

Rank : Multi-chip structure

DIMM의 하나의 rank는 8개의 chip으로 구성된다. DIMM은 한번의 memory operation에 64bit를 전송할 수 있도록 bus가 구성된다. DRAM chip의 data bus는 8bit width를 가지기에, 따라서 8개의 칩이 그림 Fig 5.처럼 DIMM의 64 bit bus를 8등분하여 차지한다. Bus를 sharing하는 multi-bank와 다르게, multi-chip 구조는 bus를 sharing하기 않고 dedicately 차지하고 있다. 이를 통해 8개의 칩에 동시에 접근하여 데이터를 읽어오는 것이 가능하다. 이를 통해 memory bus의 bandwidth를 chip 한 개 대비 8배로 확장시켰다. (애초에 칩을 64bit로 안 만들고 8bit 8개로 구성하도록 만들었는지는 모르겠다. 개인적인 생각으로는 64bit chip을 만드는 것보다 8bit chip 8개 만드는 것이 수율이 더 잘나오거나 더 저렴해서 지 않을까 싶다.)

Multi-rank & Multi-DIMM structure

Fig 1. 에서 한 channel에 여러개의 DIMM이 꽂혀 있으며, 한 DIMM도 여러 개의 rank(DIMM의 앞, 뒤)들로 구성됨을 알 수 있다. Bank와 마찬가지로 여러 DIMM(rank)는 data bus를 공유하도록 설계되며, 하나의 DIMM(rank)가 data bus를 사용하지 않을 때, 다른 DIMM(rank)가 data bus를 사용할 수 있도록 구성되었다. 따라서 bank의 경우와 같이 메모리 접근 latency를 숨기는 효과를 얻을 수 있다.

Multi-channel structure

Fig 6.는 DRAM의 multi-channel 구조를 나타낸 것이다. Fig 6는 2 channel들로 구성되며, 각 channel은 독립적인 memory operation이 가능하다. (그림에서는 memory controller가 2개 존재하는데 하나로 표현하는 경우도 있다. 자세한 내용은 memory controller 설계에서 정리해야 겠다.) 이 경우에는 data bus가 2배가 되어 데이터 전송 속도도 최대 2배가 될 수 있다. Multi-bank 개념과 같이 access latency를 줄이는 것보다는 data bus를 늘리는 효과가 있으며, 뿐만 아니라 다른 memory operation을 내릴 수 있기에 동시에 두 가지 다른 일을 할 수 있다.

Reference

[1] Sudeep Pasricha, ECE 554 Computer Architecture Lecture 5, Colorado State University, Spring 2013

[2] Todd Mowry and Brian Railing, Addressing the Memory Wall, Parallel Computer Architecture and Programming, CMU, 15-418/15-618, Fall 2016

'Semiconductor > RAM' 카테고리의 다른 글

| SRAM 구조 및 읽기와 쓰기 방법 (0) | 2022.07.22 |

|---|---|

| DRAM Memory Organization - 1 : 소개 (0) | 2022.03.27 |

| RAM 메모리 : DRAM vs SRAM (2) | 2022.03.25 |