| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- GPU

- C++

- 클라우드

- 쿠버네티스

- Compression

- Qubit

- quantum_computing

- Semiconductor

- sycl

- POD

- cloud

- DRAM

- SpMM

- FPGA

- convolution

- stl

- nvidia

- 반도체기초

- 반도체

- jhVM

- CUDA

- dnn

- jhDNN

- HA

- kubernetes

- deep_learning

- flash_memory

- CuDNN

- 양자역학의공준

- 딥러닝

- Today

- Total

Computing

SRAM 구조 및 읽기와 쓰기 방법 본문

이전글

2022.03.25 - [Semiconductor/메모리반도체] - RAM 메모리 : DRAM vs SRAM

이전글에서 DRAM(Dynamic Random Access Memory) 반도체와 비교하여 SRAM(Static Random Access Memory) 반도체의 특성에 대하여 정리하였다. DRAM과 SRAM 모두 RAM(Random Access Memory)으로 임의 위치 데이터 접근 시간이 동일하게 소모된다. 또한 둘다 휘발성 반도체로 DRAM과 SRAM 모두 전원이 연결된 상태에서만 자동한다.

오늘은 DRAM에 비해, 빠르지만 저용량인 캐쉬메모리나 레지스터에 적합한 SRAM에 대하여 정리해보고자 한다. 포스텍 강석형 교수님의 강의 시스템 반도체 설계를 바탕으로 정리하였다.

SRAM 구조 - SRAM 패키지의 Ports

Fig 1.은 SRAM chip의 ports 구성을 나타낸 것이다. A는 Addres, I는 Input, O는 Output, CS는 Chip Select, OE는 Output Enable, WE는 Write Enable을 나타낸다. SRAM은 지정된 주소(address)의 cell들에 data를 쓰거나, 저장된 data를 읽는 기능을 수행한다.

Address inputs wires는 SRAM의 주소 입력을, Data inputs wires는 입력 데이터를, Data outputs wires는 출력 데이터를 위한 wires이다. N개의 A 포트는 address 신호를 받으며, D개의 I 포트는 입력 데이터 신호를 받는다. D개의 O 포트는 출력 데이터 신호를 내보낸다. N은 주소의 길이, D는 데이터(word)의 길이를 의미한다. 주소의 길이가 N일 때 2^N개의 wordline을 가질 수 있다.

Control inputs에는 CS, OE, WE가 있다. CS가 low level이 될때, 해당 SRAM Chip에 Read/Write operation을 수행할 수 있다. OE가 low level이 될 때, Data outputs wires에 데이터가 출력된다. WE가 low level이 될때, Data inputs으로 들어온 데이터가 chip내에 저장된다.

SRAM 구조 - Cell의 배열

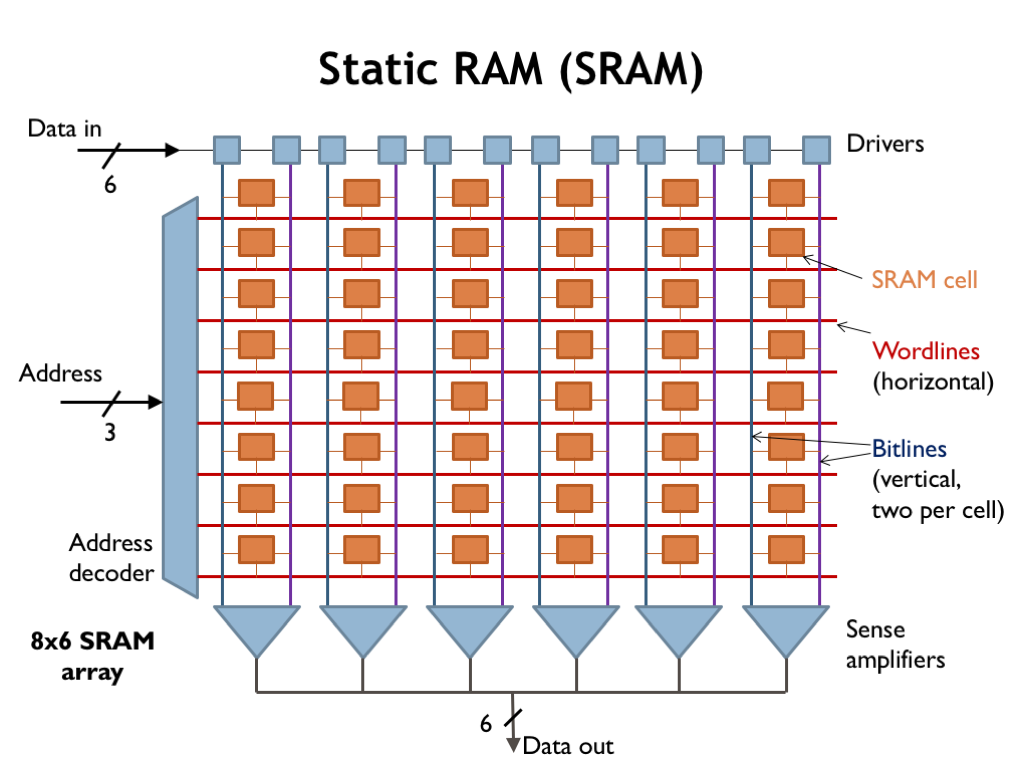

Fig 2.은 SRAM cell array의 구조를 나타낸 그림이다. SRAM은 수 많은 cell들의 배열로 구성되며, cell들은 Wordline, Bitlines으로 연결되어 있다. Fig 2. 예제는 N=3인 주소, D=6인 word(data)를 사용한다. 데이터는 word단위로 SRAM에 쓰이거나 읽혀지는데, 여기서는 6개의 bit(=cell)들이 하나의 word를 이루고 있다.

Address는 Address decoders에 의해 해석되어 8개의 wordline 중 하나를 활성화한다. 활성화된 wordline에 저장된 6개의 cell들에 데이터가 쓰이거나 읽혀진다. 쓰여질 데이터는 bitline으로 cell에 전달되며, 마찬가지로 읽혀질 데이터는 bitline을 통해 cell에서 sense amplifier에 전달된다. Sense amplifiers는 cell 신호를 증폭시키는 역할을 한다.

SRAM 구조 - SRAM Cell

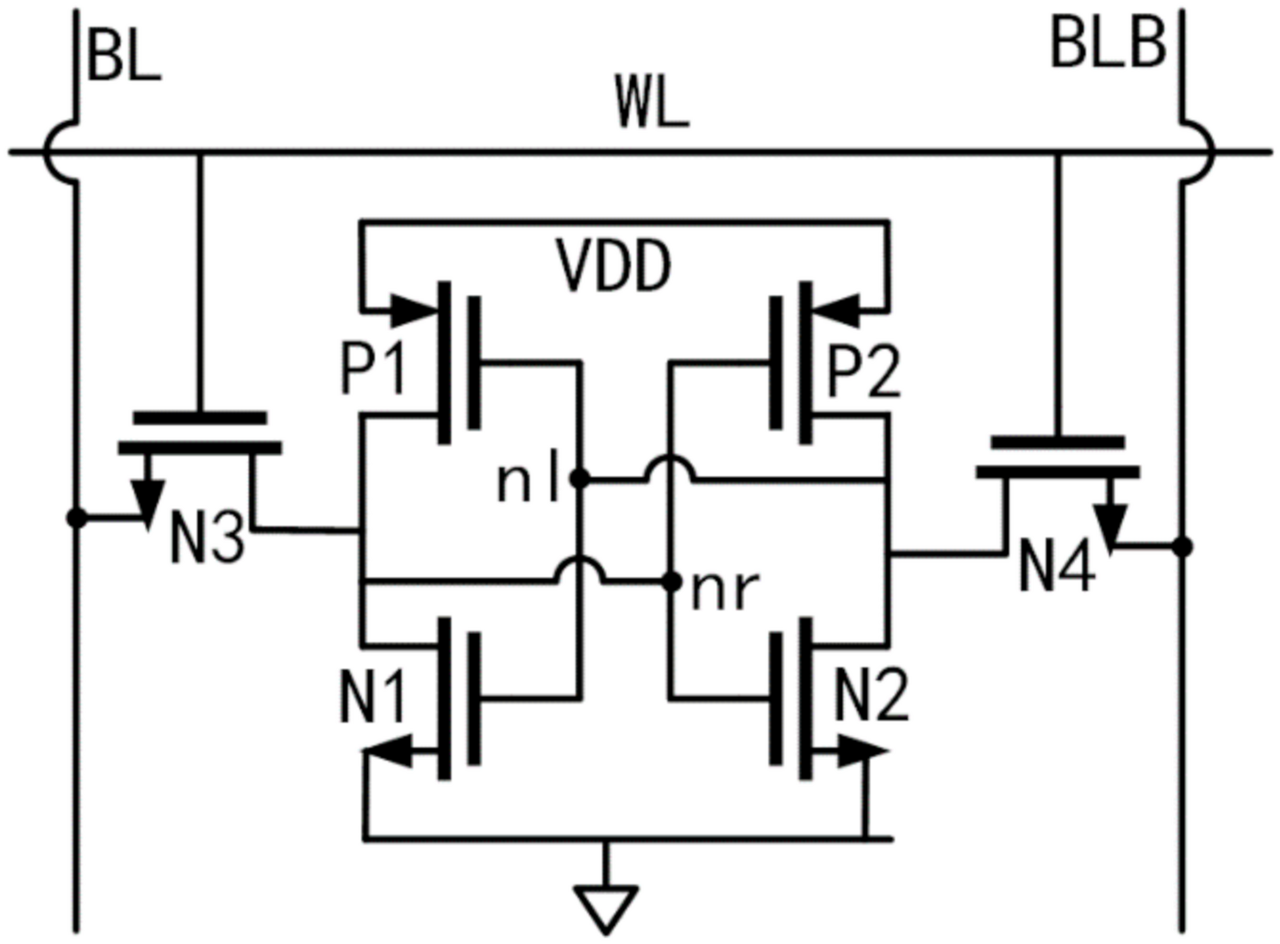

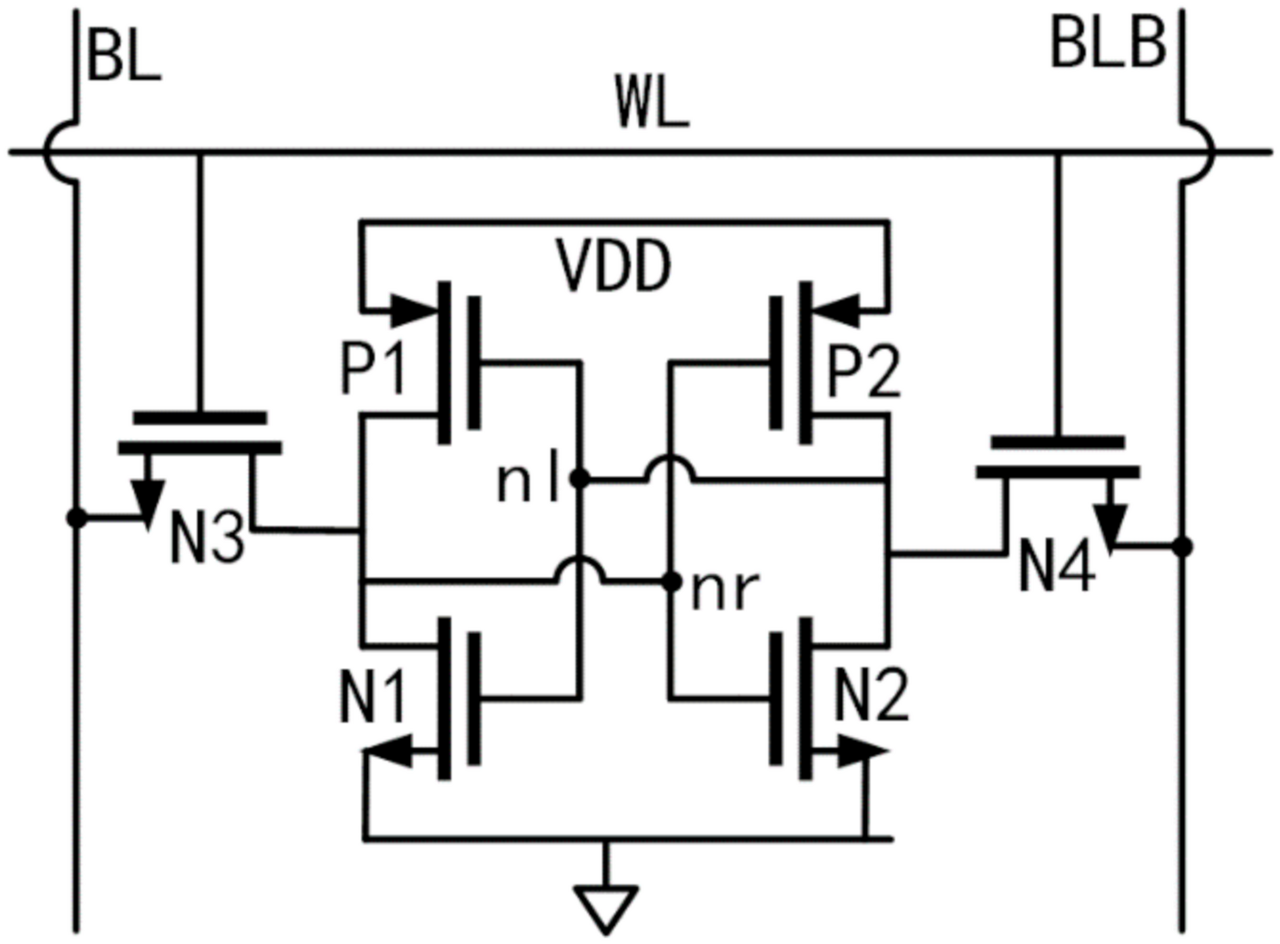

SRAM의 각 cell은 internal feedback 구조를 가지고 있으며, 전원이 공급되는 한 cell에 저장된 값을 유지할 수 있다. Fig 3.는 SRAM을 구성하는 cell의 구조를 나타낸 그림이다. 실제 cell은 Fig 3.의 왼쪽(Transistor diagram) 그림과 같이 6개의 transistor로 구성되는데, 이 구조는 오른쪽의 Inverter diagram과 구조적으로 동일하다.

한 cell은 1개의 wordline과 2개의 bitlines들로 제어된다. 2개의 bitline 각각은 bitline과 bliline_bar로 불리는데, 두 bitline은 서로 상반된 bit를 가진다(bitline이 0이면, bitline_bar는 1).

Wordline은 cell과 bitlines들을 연결하는 switch 기능을 담당하는데, wordline에 의해 제어되는 2개의 transistor를 pass transistor(gate)라고 한다. Wordline이 활성화되면 두 pass transistor가 on되어 cell과 bitlines이 연결되어, cell 내에 데이터를 쓰거나 읽을 수 있다.

SRAM 읽기

SRAM 읽기 과정은 다음과 같다.

1. Precharge BL, BLB

2. Turn on WL

3. One of the two bitlines will be pulled down by the cell

예를 들어, cell에 0이 저장되어 있다고 하자. 즉 cell의 왼쪽 영역(A)은 0을, cell의 오른쪽 영역(A_bar)은 1을 저장하고 있다. N1은 A_bar(=1)에 의해 on되어 A 영역은 ground와 연결된다. 반대로 P2는 A(=0)에 의해서 on되어 A_bar는 VDD와 연결된다. 따라서 A는 계속 0을, A_bar는 계속 1을 유지하게 된다.

이때 cell을 읽고자 한다. 일단 BL과 BLB를 1로 precharge한다. 이후 읽고자하는 wordline에 1 신호를 보내면 N3와 N4가 on되면서 bitlines과 cell이 연결된다. 이때 A와 BL이, A_bar와 BLB가 연결된다. A는 0이기에 BL의 신호는 약간 변하게 된다. 반대로 A_bar와 BLB는 모두 1이기에 신호의 변화가 없다.

이 신호의 변화를 감지하여, BL wire에 신호 변화가 생기면 0이 저장됨을, BLB wire에 신호 변화가 생기면 1이 저장됨을 알 수 있게 된다.

이때 중요한 것은 읽는 신호에 의해 cell의 값이 변하게 되면 안된다는 것이다. 즉 BL 신호가 A 신호를 바꾸면 안되기에 N1(N2)의 크기가 N3(N4)보다 크도록 설계한다.

SRAM 쓰기

SRAM 쓰기 과정은 다음과 같다.

1. Drive one bitline high, the other low

2. Turn on wordline

3. Bitlines overpower cell with new value

예를 들어, cell에 1을 저장하고자 한다. 즉 A에 1을, A_bar에 0을 저장하고자 한다. BL은 1, BLB는 0 신호를 보낸다. Wordline에 의해 N3, N4가 on되면 BLB에 의해 A_bar는 0이 된다. 따라서 P1은 on되고 N1은 off되며 A는 VDD와 연결된다. 따라서 A에는 1이 저장된다.

이때 중요한 것은 cell의 값이 BL(BLB)에 의해서 변해야 한다는 것이다. 따라서 N3(N4)의 크기를 P1(P2)보다 크게한다. 앞서 read 과정에서 N1(N2)보다 N3(N4)가 작도록 설계하였기에, 0의 신호가 1로 바뀌지는 않는다. 하지만 N3(N4)의 크기를 P1(P2)보다 크게 하였기에 1의 신호는 0으로 바뀔 수 있다.

SRAM sizing

정리하자면 SRAM cell의 6개의 transistor의 크기는 N1 > N3 > P1 (N2 > N4 > P2)여야 한다. SRAM 설계 시 이러한 constraint를 만족해야 Read & Write 시 제대로된 동작이 가능하다.

쉽게 정리하자면 다음과 같다. SRAM cell에는 2개의 값(A, A_bar 영역)이 저장될 수 있고 두 값은 항상 상반된다(01 or 10). 이때 값이 0이라는 것은 ground에 연결되었다는 것이고, 1이라는 것은 VDD에 연결되었다는 것을 의미한다.

읽기 시, 두 bitlines(BL, BLB)는 모두 1의 상태를 가진다. 이때 cell 내 0인 값 영역의 값을 변화시키면 안된다. 따라서 ground와 연결된 NMOS transisor가 가장 큰 크기를 가진다.

쓰기 시, 두 bitlines(BL, BLB)는 0 또는 1의 상반된 값을 가진다. 이때 cell의 값을 변화시키고 싶으면 cell 내 1인 값을 변화(1->0으로)시켜야 한다. 그러면 자동으로 0인 값도 1로 변화된다. 따라서 VDD와 연결된 PMOS transistor의 크기가 가장 작아야 한다.

Reference

[1] http://www.kmooc.kr/courses/course-v1:POSTECHk+EECE490F+2022_T1/about

[2] https://computationstructures.org/lectures/caches/caches.html

[3] https://en.wikichip.org/wiki/static_random-access_memory

[4] Zhang, X.; Jiang, C.; Dai, G.; Zhong, L.; Fang, W.; Gu, K.; Xiao, G.; Ren, S.; Liu, X.; Zou, S. Improved Performance of SRAM-Based True Random Number Generator by Leveraging Irradiation Exposure. Sensors 2020, 20, 6132. https://doi.org/10.3390/s20216132

'Semiconductor > RAM' 카테고리의 다른 글

| DRAM Memory Organization - 2 : 성능 향상 전략 (0) | 2022.03.31 |

|---|---|

| DRAM Memory Organization - 1 : 소개 (0) | 2022.03.27 |

| RAM 메모리 : DRAM vs SRAM (2) | 2022.03.25 |