| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

- FPGA

- jhVM

- convolution

- C++

- GPU

- CUDA

- 반도체

- deep_learning

- quantum_computing

- 클라우드

- flash_memory

- DRAM

- dnn

- SpMM

- kubernetes

- jhDNN

- 반도체기초

- Semiconductor

- 딥러닝

- nvidia

- cloud

- POD

- 쿠버네티스

- stl

- CuDNN

- Compression

- HA

- Qubit

- sycl

- 양자역학의공준

- Today

- Total

Computing

[반도체 소자] 커패시터 Capacitor 기본 정리 본문

이전 포스터에서 P형 반도체와 N형 반도체의 특성 및 그것들의 접합하여 만든 P-N 접합 다이오드 (P-N junction diode)에 대하여 정리하였다. 이번 포스터에서는 P형, N형 반도체 및 P-N 접합 특성을 활용한 또 다른 소자인 커패시터에 대하여 정리하고자 한다.

커패시터 Capacitor

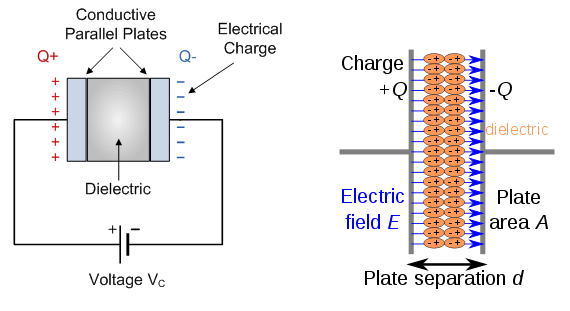

커패시터, 축전기는 전기전자회로에서 전기 용량을 전기적 퍼텐셜 에너지로 저장하는 장치[1]로, 쉽게 생각하여 전기를 저장하는 소자이다. Fig 1. 왼쪽 그림은 커패시터를 나타낸 모형도로 두 개의 판(plates) 사이에 유전체(dielectric)을 넣어서 만들어진다. 두 개의 판에 Vc의 전압을 인가할 경우, 유전체에는 Q만큼의 전하량이 저장된다.

커패시터에서 전기가 실제로 저장되는 물질이 바로 유전체이다. 유전체는 절연체와 같이 전기가 흐르지 않지만, 전기장 속에서 극성을 지니게 되는 절연체이다. Fig 1.의 오른쪽 그림은 전기장 속에서의 유전체 특징을 잘 나타낸 것으로, 전기장의 방향에 따라 유전체 내 전기 쌍극자가 정렬되면서 표면에 전하를 띄게 된다. 이때 유전체에 얼마나 많은 전하를 저장할 수 있는 지를 나타내는 물질의 특성을 유전율 ε이라 하며, 유전율이 높을수록 해당 커패시터가 저장할 수 있는 전하량이 증가[4]한다.

전기 용량 (커패시턴스, capacitance)은 단위 전위차에 의해 커패시터에 저장되는 전하량을 의미하며 단위는 F(패럿)이다. 전기 용량을 C, 저장되는 전하량을 Q, 커패시터에 인가된 전압을 V, 커패시터의 넓이 A, 두 판 사이의 거리 S, 유전체의 유전율 ε이라 할 때 다음 Eq 1.과 같이 표현된다.

Eq 1.에서 보듯, 커패시터의 특징, 어떤 유전체를 사용하고, 크기를 어떻게 할 지에 따라서 커패시터가 저장할 수 있는 전기 용량이 달라진다. 이때 반도체를 이용하여 커패시터를 구현할 수 있는데, 반도체를 사용하여 커패시터를 구현할 시 커패시턴스를 가변할 수 있어 좋다. 반도체를 이용한 커패시터는 크게 2가지, 접합 커패시터와 MOS 커패시터로 나뉜다.

접합 커패시터

접합 커패시터는 PN 접합 시 생기는 공핍층의 특성을 이용하여 전기를 저장하는 커패시터이다. Fig 2.는 접합 커패시터의 원리를 잘 보여주는 그림이다.

PN 접합 시, 접합면을 따라 자유전자와 정공의 charge carriers가 사라진 공핍층이 생긴다. 공핍층 내에는 donor와 acceptor 원자들은 여전히 남아있기에 P형 반도체의 공핍층은 (-)극으로, N형 반도체의 공핍층은 (+)극으로 전도된다. 따라서 공핍층은 유전체 역할을, carriers가 남아있는 P형, N형 반도체 영역은 도체(plates) 역할을 한다. 이러한 PN 접합 특징을 이용해 전기를 저장할 수 있게 된다.

Eq 1.에서 알 수 있듯, 두 plates 사이의 거리 S에 따라 전기 용량이 변한다. 접합 커패시터에서도 마찬가지로, 공핍층의 폭 S에 따라 전기 용량이 변한다. 따라서 접합 커패시터에 전압을 인가하여 공핍층의 폭을 조절하면 커패시터의 전기용량을 조절할 수 있다.

MOS 커패시터

MOS 커패시터는 Metal - Oxide - Semiconductor (금속 - 산화물 - P or N형 반도체)로 만들어진 커패시터를 의미한다. 금속과 반도체는 도체의 역할을, 산화물은 유전체의 역할을 수행한다. Fig 3.은 MOS 커패시터를 나타낸 그림이다.

MOS 커패시터는 금속(Gate)에 인가하는 게이트 전압에 따라서 커패시턴스가 변한다. Fig 4.는 게이트 전압에 따른 커패시터 내 전압의 변화를 나타낸다.

Fig 4.에서 보듯 게이트 전압이 (-)일 경우, 산화물 영역이 유전체가 되어 전하를 저장한다. 이때는 게이트 전압에 상관없이 산화물의 유전율과 커패시터의 크기(유전체 폭과 넓이)에 따라서 전기 용량이 결정된다.

그에 비해 (+) 전압이 인가될 경우, 조금 더 복잡해진다. (+) 전압이 인가될 경우 P형 반도체에는 공핍층이 생기게 된다. 앞서 접합 커패시터에서 공핍층이 유전체 역할을 할 수 있음을 확인하였는데, 마찬가지로 P형 반도체 내 공핍층이 추가적인 유전체 역할을 수행한다. 따라서 2개의 커패시터가 직렬로 연결한 것과 같은 효과를 낸다. 게이트 전압이 강해질수록 공핍층의 폭이 두꺼워지기에 Cd는 감소하게 된다. 이를 통해 MOS 커패시터의 전기 용량을 조절할 수 있다.

추가적으로 직렬 연결된 전기 용량은 Eq 2.로 구할 수 있다.

P형 반도체를 이용한 MOS 커패시터의 전압 V에 따른 전기 용량 C의 변화를 정리하면 Fig 5.와 같다.

Reference

[1] https://ko.wikipedia.org/wiki/%EC%B6%95%EC%A0%84%EA%B8%B0

[2] https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=pro_000&logNo=220728196521

[3] https://ko.wikipedia.org/wiki/%EC%9C%A0%EC%A0%84%EC%B2%B4_(%EB%AC%BC%EB%A6%AC%ED%95%99)

[4] http://www.ktword.co.kr/test/view/view.php?m_temp1=1384

[5] 엄우용, 이선우, 이공계 학생을 위한 핵심 반도체 개론, K-MOOC

[6] http://www.ktword.co.kr/test/view/view.php?m_temp1=4500

'Semiconductor > 반도체개념' 카테고리의 다른 글

| [반도체 소자] 트랜지스터 기본 정리 (바이폴라 트랜지스터, MOSFET) (0) | 2022.06.29 |

|---|---|

| [반도체 소자] 저항기, PN 접합 다이오드 기본 정리 (0) | 2022.06.23 |

| 반도체 기초 (6) 외부의 자극에 의한 Carriers의 운동 (Drift & Diffusion) (0) | 2022.06.10 |

| 반도체 기초 (5) Carriers의 특징 - 유효 질량, Scattering, Mobility (0) | 2022.06.07 |

| 반도체 기초 (4) Charge Carriers와 Fermi Energy의 관계 (0) | 2022.05.27 |